Implementation with other class of devices, like 71LS161/163 will not beĬonsidered. This flip flops come in Dual-Packages so all you need is two of them. Design and simulation of a four-bit Up-Down counter you will need to useįlip-Flops JK negative edge triggered 74112. Analysis, including comments and conclusionsĢ. Waveform in the same order of variables that you provide in the truth tables. Do as many simulations youĬonsider that show the functionality of the circuit. The waveform resulting from the time simulation. The written description of the circuit, especially those that appear in logical Add labels for any interior signals that appear in Make sure all input and output connectors are labeled Of any unusual problems you had and how you solved them This section should also contain a description It should refer to the detailed documentation (such as It should explain design techniques if theyĪre not self explanatory. Maps or algebraic simplifications you performed, and any tables or stateĭiagrams for sequential circuits. It should contain any logical expressions you use, any Karnaugh Design details: This subsection is where you can go into the details of yourĭesign. Implemented, any conditions or restrictions the user must observe to use theĬircuits, and the high level structure of your circuits at the block diagram level. For example, you could explain any algorithms you That is to give a high level description of what your circuits doĪnd how they do it. This should be an expanded version of the Theory of operation: Explain how your circuit works, but do not give Objective: Design and simulate a 4-bit Synchronous Up-Down Counter in Quartus II.Įach student will turn in a report with the results of their design and simulation of the (Please do this) Each student will turn in a report with the results of their design and simulation of the circuits.(SEE Attached Project Guidelines Document for report details and all project requirements).

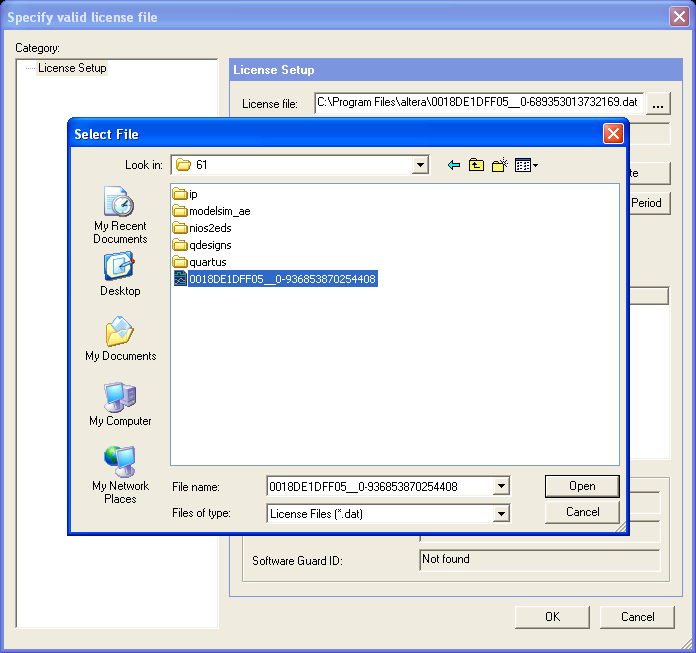

Altera quartus ii for students pdf#

(SEE Attached PDF for Project Counter examples) Bonus points implementing with ALTERA boards DE2-115. You need to take into consideration the following: a) The simulations should use a clock of 25 MHzb) The snap shots should show a complete count (from 0000 to 1111 and another for a count from 1111 to 0000), and should show uses of Asynchronous Clear and Preset. Implementation with other class of devices, like 71LS161/163 will not be considered.

The project involves using Altera Quartus® II CAD system and proceeding with the following requirements: Design and simulation of a four-bit Up-Down counter you will need to use Flip-Flops JK negative edge triggered 74112.

0 kommentar(er)

0 kommentar(er)